WP2: Computing System on Chips (SoCs)

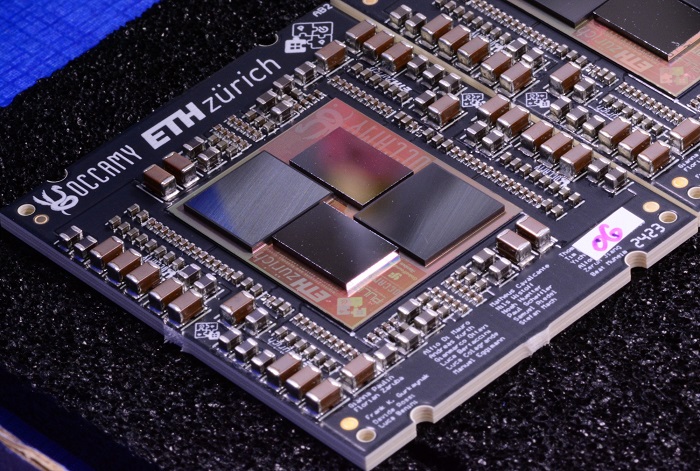

WP2 will strengthen Switzerland’s research in the design of high-performance, low power, secure and safe computing chips and systems, while securing long-term paths for open innovation and international collaboration, worldwide and with the EU as privileged partner. More specifically, efficient and scalable open-source RISC-V processors and post-quantum cryptographic computing cores, as well as solutions for power and thermal-aware SoC designs will be developed.

Performance requirements keep growing across the computing continuum, from wearables to supercomputers. While for several decades computing performance has relied upon silicon technology scaling, today we clearly see diminishing returns: only 10x improvement of performance over 12 years, while application requirements are accelerating to 10x over 2-3 years. In order to tackle this challenge, the design of computing chips must embrace full-stack, application-to-technology co-design approaches. At the same time, the pervasiveness of computing in life-critical functions (e.g., for autonomous driving, traffic control, communication systems, etc.) prompts for an increased research emphasis on security, as well as predictability, reliability, and safety. Furthermore, the current geo-political trend toward increased decoupling and sovereignty of global international competitors (EU, USA, China, Japan, and India) in the field of high-performance computing is creating an increasingly challenging research environment, especially for smaller countries like Switzerland, which must find ways to collaborate with larger partners trying to avoid captivity.

WP2 Lead: Prof. Luca Benini, ETH Zurich

Luca Benini is head of the Digital Circuits and Systems Group at ETH Zurich. His group focuses on energy efficiency for digital circuits over a very wide operating range, from small devices with a power budget of less than a mW that will drive Internet of Things (IoT) applications, all the way to High Performance Computing (HPC) systems, such as data centers that consume power in the MWs.

Contact: Luca Benini

WP2 Co-lead: Dr. Miguel Peon, EPFL

Miguel Peon is the sustainable computing systems manager at external page EcoCloud, EPFL.

Contact: external page Miguel Peon

Task Leaders & Senior Collaborators

- external page Prof. David Atienza, EPFL, WP2 & co-PI WP6

- external page Prof. Thomas Bourgeat, EPFL

- external page Prof. Edouard Bugnion, EPFL

- external page Dr. Jean-Luc Nagel, CSEM

- external page Dr. Stéphane Emery, CSEM, WP2 & PI WP6

Students & Researchers

- external page Kai Zhu, PhD student, Supervisor: Prof. David Atienza

- external page Dr. Darong Huang, Postdoc, Supervisor: Prof. David Atienza

- external page Leslie Xu, PhD student, CSEM/EPFL, Supervisors: Dr. Jean-Luc Nagel, Prof. Andreas Burg

- Navaneeth Kunhi Purayil, PhD student, Supervisor: Prof. Luca Benini

- Christopher Reinwardt, PhD student, Supervisor: Prof. Luca Benini

- Enrico Zelioli, PhD student, Supervisor: Prof. Luca Benini

- Zexin Fu, PhD student, Supervisor: Prof. Luca Benini

- external page Charly Castes, PhD student, Supervisor: Prof. Edouard Bugnion

- external page Dr. Yann Herklotz, Postdoc, Supervisor: Prof. Thomas Bourgeat

- external page Rui Yang, PhD student, Supervisor: Prof. Edouard Bugnion