WP1: IC Design Infrastructure

WP1 will link Swiss IC design support activities under one banner, with prototyping support for SwissChips partners, including a network to share IC design information, training tutorials and workshops, and funding to cover prototyping costs. WP1 will also support outreach activities for open-source IC design, as well as showcase SwissChips IC design at various events.

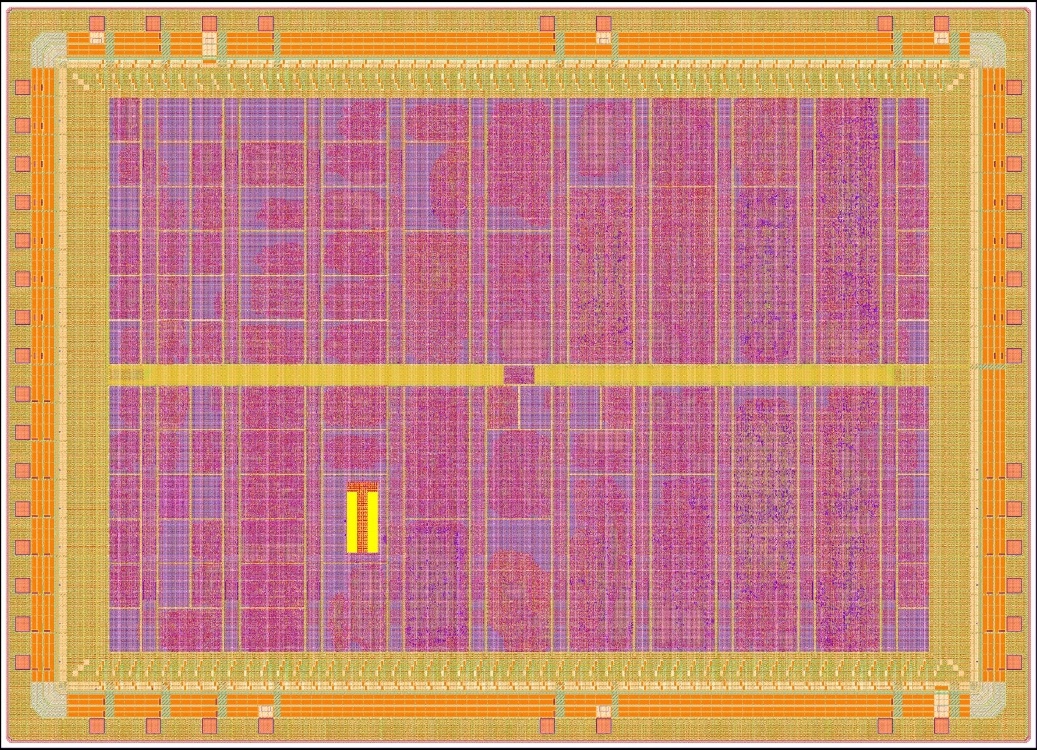

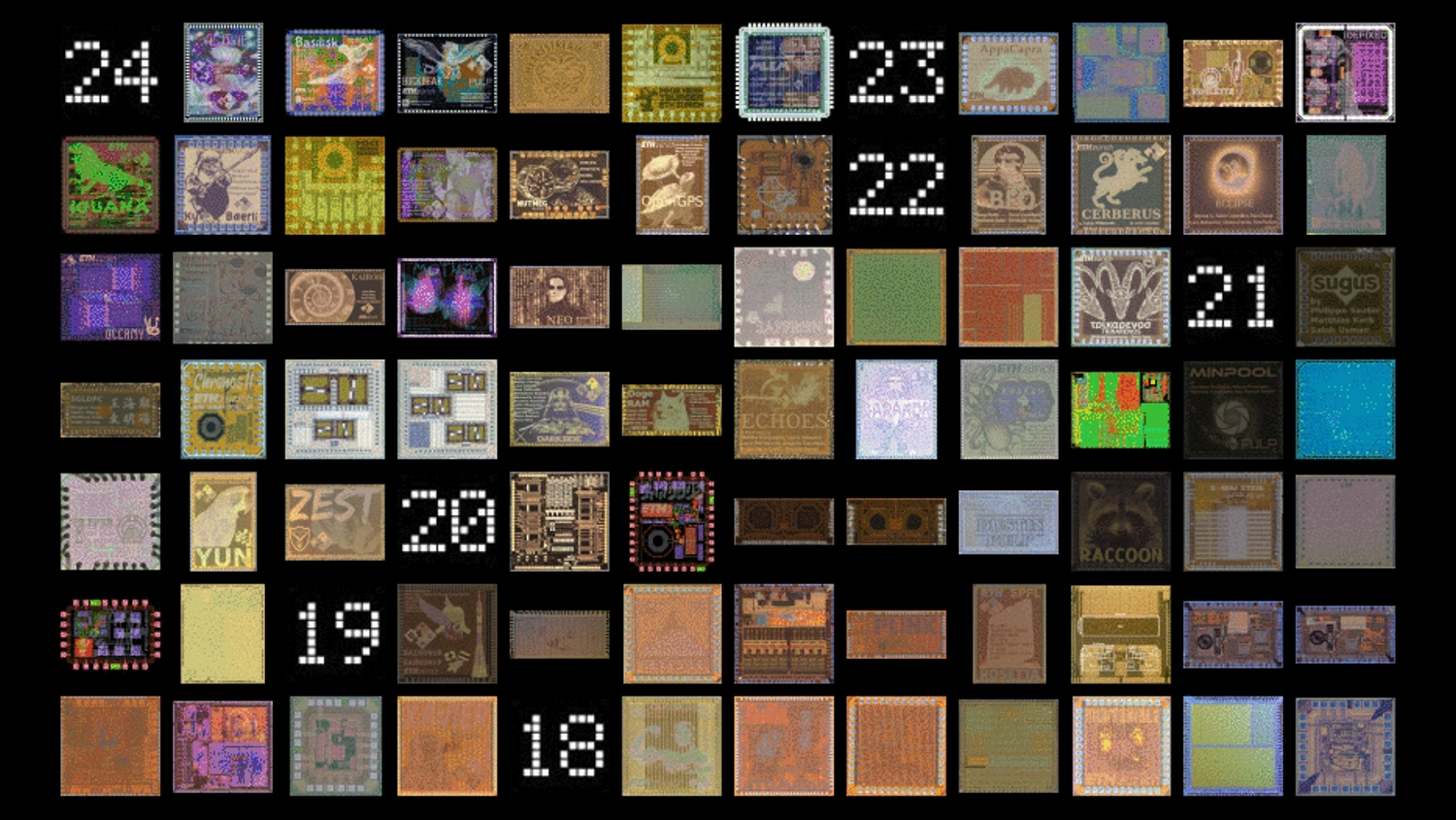

See our latest chips in our Chip Design Gallery

The goal of WP1 is to link Swiss IC design support activities under one banner. This includes supporting SwissChips partners as well as other Swiss universities and universities of applied sciences with their tape-outs, sharing know-how, making use of and fostering open-source approaches for IC design, preparing tutorials and summer schools for IC design topics, helping each other with EDA design flows, working together to have access to state-of-the-art IC manufacturing technologies, discussing solutions with technology and EDA tool vendors for SwissChips, and supporting a shared design platform within Switzerland. As part of this WP, existing institutions within each partner will form a technical network in order to closely collaborate on finding solutions for all SwissChips partners.

WP1 will work with external page Tiny Tapeout to support outreach activities and provide shuttles for SwissChips, bringing open-source IC design to students and enthusiasts through chip design tutorials and workshops. WP1 will also disseminate SwissChips IC design through various channels and events, including our annual SwissChips event where we will showcase our technical work and provide a networking platform for researchers and industry, and everyone in Switzerland interested in IC design.

WP1 Lead: Frank K. Gürkaynak, ETH Zurich

Frank Gürkaynak is a Senior Scientist in the Digital Circuits and Systems Group of the Integrated Systems Laboratory (IIS) at ETH Zurich, and the Director of the Microelectronics Design Center (DZ) which provides design tools, know-how and licenses for ASIC, FPGA, Embedded Systems and PCB design supporting research and teaching at D-ITET.

Contact: Frank K. Gürkaynak

WP1 Co-lead: Dr. Alexandre Levisse, EPFL

Alexandre Levisse is an IC Design Specialist and EDA Team-Lead in the external page Embedded Systems Laboratory (ESL) at external page EPFL. His work is focused on providing design enablement and consulting services on IC design for EPFL laboratories, training and education for researchers, engineers and students, and software asset management on EDA tools, technologies and IPs.

Contact: external page Alexandre Levisse

WP1 Collaborators, Students & Researchers

- external page Robin Leplae, IC design engineer, EDA support, Supervisor: Dr. Alexandre Levisse

- external page Dr. Davide Schiavone, computer architecture and open-source IC design, Supervisor: Dr. Alexandre Levisse

- external page Alex Widerski, graphical designer, communication, Supervisor: Dr. Alexandre Levisse

- external page Jakub Salko, IT support for EDA, Supervisor: Dr. Alexandre Levisse

- Beat Muheim, IC Design Flows, Supervisor: Dr. Frank Gürkaynak

- Zerun Jiang, IC Design Flows, Supervisor: Dr. Frank Gürkaynak

- Alfonso Blanco, PCB Design, Supervisor: Dr. Frank Gürkaynak

- Arianna Rubino, IC Design Flows, Supervisor: Dr. Frank Gürkaynak

- Xinling Yue, IC Design Flows, Supervisor: Dr. Frank Gürkaynak

IC Design Applications:

SwissChips will support the manufacturing costs for selected IC designs for research and teaching projects. We accept applications from researchers at Swiss universities and universities of applied sciences to support full or part of the manufacturing costs for your project.

Our technical evaluation committee, consisting of six members from universities, university of applied sciences and research centers, will review and evaluate applications quarterly, and for smaller budgets, on a rolling basis.

The next evaluation will take place April 20th 2026. Please submit your applications by mid-April to be considered for this next round.

We will also evaluate applications for smaller budgets on a rolling basis, provided they meet the following criteria:

- the requested amount is not more than CHF 25'000,

- the institution of the project team is a Swiss university or university of applied science and must be external to the SwissChips partner institutions (ETH Zurich, EPFL, CSEM),

- complete application information is received using our template (below).

Application process:

Please prepare a short (1-2 page) application detailing the design and costs [Template (DOCX, 14 KB)]

Tiny Tapeout for SwissChips: Open-source IC design for everyone

Tiny Tapeout is supporting SwissChips with outreach activities, bringing open-source IC design to students and enthusiasts through chip design tutorials and workshops. Read more on our Tiny Tapeout page.