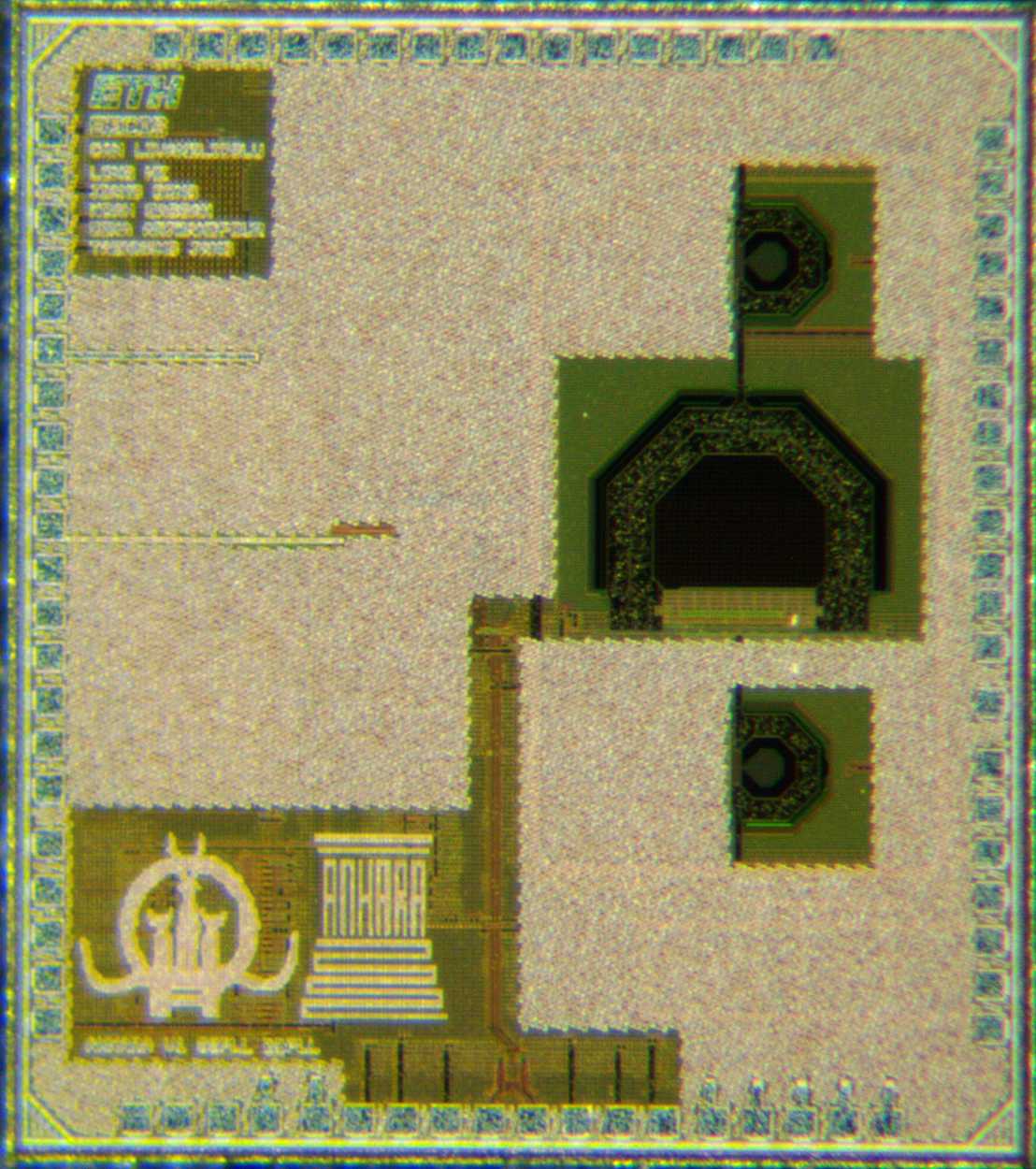

Ankara

Design: Ankara is a PLL-XO co-design introduced to address the limitations of conventional frequency generation and synthesis approaches, which treat the crystal oscillator (XO) and phase-locked loop (PLL) as separate entities. The proposed design establishes a bidirectional signal flow, where the XO provides a clean reference to the PLL and the PLL precisely controls pulse-injection timing for the XO driver, ensuring current is injected at the optimal low-Impulse-Sensitivity-Function (ISF) regions of the XO for noise and power efficiency.

Ankara integrates an on-chip, PLL-controlled pulse-injection XO driver with a 96MHz fundamental-tone piezo-electric crystal with 8Ω equivalent series resistance and 10pF load capacitance on PCB. A small Pierce oscillator assists in crystal start-up before handing over control to two pulse-injection drivers. The PLL receives a single-ended reference via a low-power reference buffer, which eliminates short-circuit currents at switching transients to minimize power consumption and jitter. A cascoded pull-down NMOS is introduced to mitigate the Miller effect, enhancing input slope and stability. A fully differential sub-sampling PLL (SSPLL) is implemented, featuring a primary-secondary sample-and-hold phase detector, a gm-stage (OTA), an on-chip loop filter, and a low-supply class-D LC voltage-controlled oscillator (VCO).

This co-design integrates efficient power management, precise timing control, and noise reduction techniques, leading to enhanced PLL-XO co-operation and co-optimization and improved performance. It achieves 53fsrms jitter and -70dBc reference spur at 4.6GHz and 7.6mW power, yielding a jitter Figure-of-Merit of -256.7dB.

Design team: Ankara was designed by Can Livanelioglu, Long He, Jiang Gong, Sina Arjmandpour, Gabriele Atzeni and Taekwang Jang, ETH Zurich

Paper: C. Livanelioglu, L. He, J. Gong, S. Arjmandpour, G. Atzeni and T. Jang, "19.10 A 4.6GHz 63.3fsrms PLL-XO Co-Design Using a Self-Aligned Pulse-Injection Driver Achieving −255.2dB FoMJ Including the XO Power and Noise", external page external page2025 IEEE International Solid-State Circuits Conference (ISSCC), 2025.

DOI: 10.1109/ISSCC49661.2025.10904568. [external page Paper: IEEE Xplore]