Chip Design

The SwissChips chip gallery highlights our latest chip designs including those from our SwissChips research and externally supported chip designs through our IC Design application process (under WP1).

SwissChips Chip Design Statistics:

Year 1 (as of July 2025):

Internal chips designed: 34

External chip designs, proposals accepted: 7

More about our application process for IC design support for research and teaching projects at Swiss universities and universities of applied sciences can be found here: WP1 IC Design

Chip Details

-

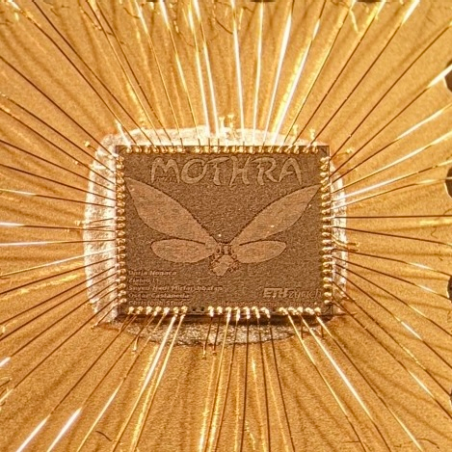

Mothra, ASIC, 2025 (IIP, ETH Zurich) -

Ankara, PLL-XO co-design, 2025 (EECIS, ETH Zurich) -

Deltasense, Bio-signal ADC, 2025 (EECIS, ETH Zurich) -

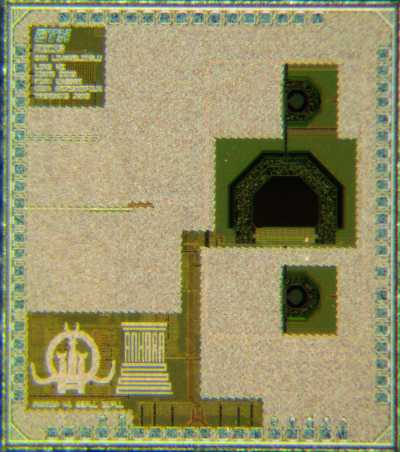

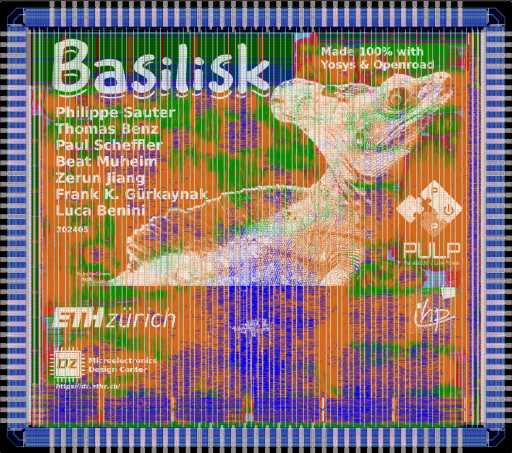

Basilisk, 2024 (PULP Platform, ETH Zurich) -

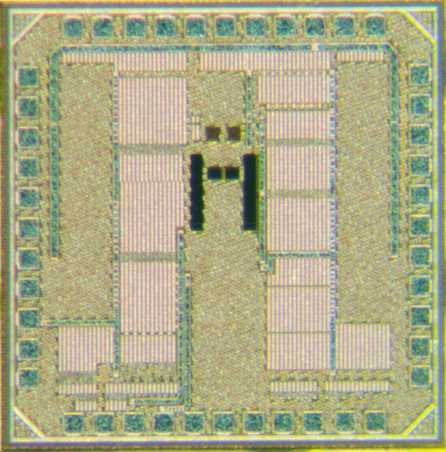

Astral, 2024 (PULP Platform, ETH Zurich) -

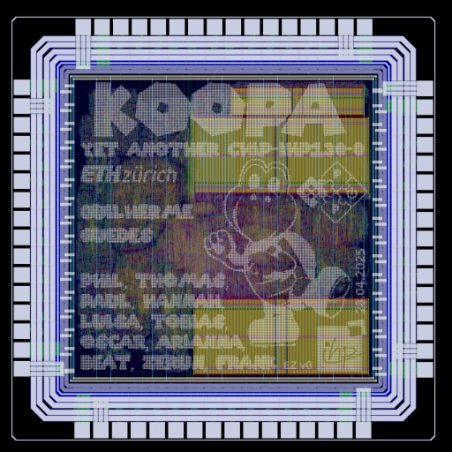

Koopa, 2025 (PULP Platform) -

Chip-4Dopamine, 2025 (BCI Lab, EPFL) -

Chip-4Brain, 2025 (BCI Lab, EPFL) -

Zervreilahorn, application-specific integrated circuit, 2025 (OST) -

M-FLOCC, 2025 (Lab of Wave Engineering, EPFL) -

Weisshorn, Cryogenic Electronics, 2025 (AQUA Lab, EPFL & NCCR Spin) -

HEEPatia, in TSMC 16nm, 2025, (ESL and TCL, EPFL, and Politecnico di Torino) -

HEEPnosis, in GF 22nm FDX, 2025 (ESL and TCL, EPFL) -

HEEPidermis, in TSMC 65nm LP, 2025 (ESL, EPFL, and Universidad Católica del Uruguay (UCU) and Politecnico di Torino) -

Infinite-Loop CMOS-Compatible Isolator, 2025 (CSEM) -

SUMON, electrochemical sensing, 2025 (CSEM) -

BELL11, 40,000-electrode microelectrode array, 2026, (Bio Engineering Laboratory, ETH Zürich)