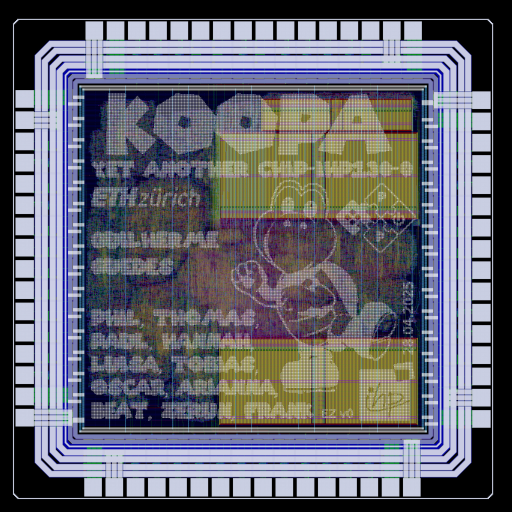

Koopa

Design: Koopa details: IIS Chip Gallery

Koopa is an end-to-end open-source chip taped out by external page PULP Platform, on IHP silicon, using The OpenROAD Project, YosysHQ, tools, with financial support support from SwissChips.

Koopa is based on the external page Croc SoC platform. Koopa in IHP 130 features a newly designed QSPI interface & uses a new open source library developed for the VLSI5 course at ETH Zurich, led by Oscar Castaneda and Christoph Studer.

Design team: Guilherme Guedes, Philippe Sauter, Thomas Benz, Paul Scheffler, Hannah Pochert, Luisa Wuethrich, Tobias Senti, Oscar Castaneda, Arianna Rubino, Beat Muheim, Zerun Jiang, Frank K. Gurkaynak

This design has received generous support from external page Leibniz Institute for High Performance Microelectronics through the BMBF project FMD-QNC (16ME0831).