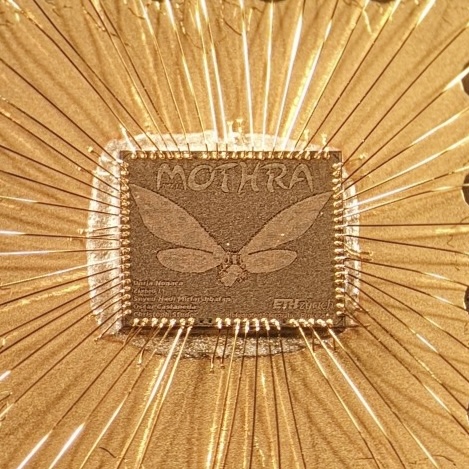

Mothra

Design: Mothra is a 22nm ASIC for data detection in mmWave massive MU-MIMO-OFDM systems. Our design implements a Gram-domain block coordinate descent algorithm with a deep-unfolding-optimized posterior mean estimate denoiser. It supports 16 UEs transmitting QPSK to 256-QAM symbols to a 128-antenna BS. Measurement results demonstrate a peak throughput of 7.1 Gbps at 367mW with a core area of only 0.97 mm², demonstrating the detector’s best-in-class throughput and area efficiency.

Design team: the ASIC was designed by Zixiao Li during his MSc Thesis in the IIP Group with Seyed Hadi Mirfarshbafan, Oscar Castañeda, Christoph Studer.

Paper: Z. Li, S. H. Mirfarshbafan, O. Castañeda and C. Studer, "A Deep-Unfolding-Optimized Coordinate-Descent Data-Detector ASIC for mmWave Massive MIMO,"external page IEEE Journal on Selected Areas in Communications, 2025.

DOI: 10.1109/JSAC.2025.3531558. [external page Paper IEEE Xplore]

Additional: The detector design was implemented on the Mothra ASIC, which is shared with a matrix preprocessing engine designed by Darja Nonaca.