Prof. Taekwang Jang's EECIS group presented two papers at ISSCC 2025

The EECIS group, ETH Zurich, led by Prof. Taekwang Jang (WP5) presented two papers at ISSCC 2025 on the new architectures on the frequency synthesizer and the direct digitization sensor interface.

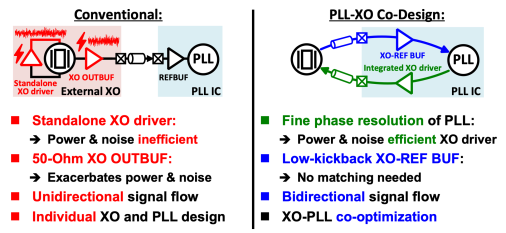

While recent PLLs have achieved <50 fs jitter with a power consumption of just a few mW, they are typically tested with ultra-low noise XOs consuming 100s to 1000s mW, overlooking holistic optimization. This paper proposes noise and power optimization for the entire frequency generation and synthesis chain. The presented PLL-XO co-design achieves 63 fs jitter and -255.2 dB FoMJ, incorporating the noise and power of the XO, reference buffer, and PLL.

Can Livanelioglu, Long He, Jiang Gong, Sina Arjmandpour, Gabriele Atzeni, Taekwang Jang: A 4.6 GHz 63.3 fsrms PLL-XO Co-Design Using a Self-Aligned Pulse Injection Driver Achieving -255.2 dB FoMJ Including the XO Power and Noise, external page 2025 IEEE International Solid-State Circuits Conference (ISSCC). Paper [external page IEEE Xplore]

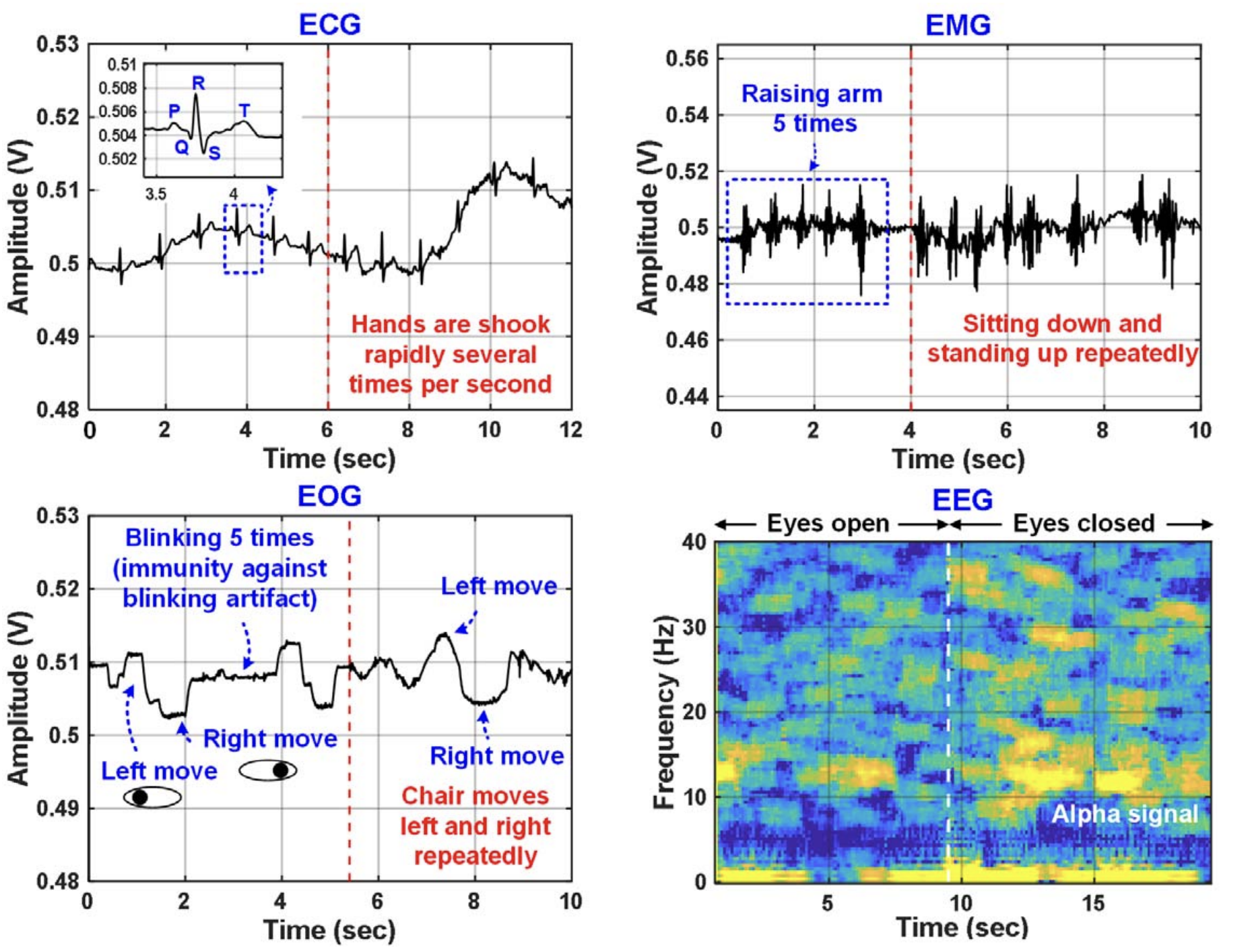

Direct digitization front-ends are emerging as alternatives to amplifier-first front-ends, offering a wider dynamic range for superior interference tolerance. However, their noise efficiency is typically much worse than amplifier-first architectures, resulting in high power consumption or increased input-referred noise. This paper introduces a delta-amplification noise-shaping SAR ADC that simultaneously achieves high noise efficiency (3.47 NEF) and wide dynamic range (92.8 dB).

Kyeongwon Jeong, Can Livanelioglu, Jiawei Liao, In-Hee Lee, Taekwang Jang: A 3.47 NEF 175.2 dB FOMS Direct Digitization Front-end Featuring Delta Amplification for Enhanced Dynamic Range and Energy Efficiency in Bio-Signal Acquisition, external page 2025 IEEE International Solid-State Circuits Conference (ISSCC). Paper [external page IEEE Xplore]